新晔电子(深圳)有限公司 518000

摘要:本文基于 FPGA和 CMOS图像传感器,使用Verilog 语言对CMOS传感器的图像信号进行采集,缓存,ISP,然后经过USB3.0传输到PC上位机进行显示,完成了对图像的整体采集方案。最后经过试验,证明该系统是正确的,有效的。本系统可用于工业检测,汽车环视,医疗影像及其他行业,具有很高的实用价值。

关键字:FPGA;CMOS;易灵思;安森美

引言

传感器是一种非常常见的光电转换的设备,它将每个物理位置上间断的采样触发点上的光强,色彩,电流大小,电压大小等信号按照特定规律转换成有矢量性质的连续数字信号。在过去的的图像传感器工艺中中,采用了光学镜头和光敏二极管完成对图像信息的采集。然而随着制程的发展,需要更高精度和更高分辨率的采集方案。因此,本文提出了一种基于FPGA和CMOS图像传感器的驱动方案。FPGA实现了sensor的图像信号的采集和处理,并对sensor进行控制;同时,对处理后的数据进行传输到上位机的操作。通过FPGA与CMOS图像传感器之间的数据交换,完成了CMOS图像传感器的驱动电路设计。这种方案具有高灵敏度、大动态范围和高色彩还原能力等优点,可用于各种图像采集应用场景

一、CMOS驱动系统设计

在 CIS驱动系统中,以sensor为中心,完成了对图像传感器的数据读取和寄存器控制写入。在此基础上,时序模块由 Verilog HDL语言编制而成,由SPI 有效图像寄存器配置,LVDS图像信号输入、LVDS图像信号同步校准三部分组成。其中,spi 读写寄存器配置信息,FPGA上电后读取ROM信息进行配置, ;LVDS共14个通道,传输奇偶两组图像数据,传输速率777.6Mbps,不间断采集;在传感器稳定工作后,FPGA判断采集的数据是否和传感器发送的一致来进行时钟相位的校准;达到一致后,即完成了CIS驱动模块的设计。

1.1sensor参数

XGS-12000 是一种集模拟图像采集、模数转换、数字信号处理于一体的 CMOS有源图像传感器。这个传感器有1200个像素,12位AD采样下,最大帧率可以达到90FPS,最高分辨率为4096*3072; 24路数据传输通道,图像有黑白和彩色两种模式,具有宽动态的超高性能:

感应器的分辨率:4096 (H) x 3072 (V)

像素大小:3.2微米*3.2微米;

感应器大小:1英寸大小;

像素输出频率:777.6Mbps;

芯片上 ADC:12位;

工作方式:全局快门(Global Shutter)。

1.2 COMS芯片的上电处理过程

传感器刚开始工作时,会在4个状态机内进行状态切换,分别为上电阶段,复位阶段,初始化阶段,最后到捕获数据阶段;

上电阶段:传感器遵循严格的上电时序,共有VDD_IO==1.8V ,VDD_PLL==2.8V,VVDD==1.8V,VAA==2.8V,VAA_PIX/VAA_PIX_BST/VAA_RD==3.0V,VDD_SLVS==0.4V/1.2V,共五组电源,每一组电源按顺序,最少需要100us的稳定时间;

复位阶段:当电源稳定后,外部晶振给传感器最小30MHz,标准32.4Mhz的时钟,最少30ms稳定后,外部控制芯片或者利用RC复位电路,将传感器的Hard Reset 拉高,对于30M的时钟来说,最少需要复位30个时钟周期,无上限要求;

初始化阶段: 复位结束,主控芯片就可以通过SPI引脚或者IIC引脚对传感器进行初始化操作,一般有500个寄存器需要配置,串口的速度一般在15Mhz;配置完寄存器,传感器会通过调用内部的PLL(锁相环模块),整个时间大约70us左右,之后就可以正常工作了);

捕获数据: 用户通过处理芯片访问读取寄存器reg=3800,只要返回的数据是0*0001,那么就代表传感器可以传输正确的图像,主控就可以开始进行图像信号的采集;

1.3 COMS芯片的工作处理过程

通常的工作 我们一般工作在流水线快门模式下,这个模式下,传感器光学部分色彩积分和读出同时进行。图像被连续读取,第N帧的积分正在进行中,同时读出前面的N-1帧。每个帧的读出始于帧开销时间(EFOT),此时将像素二极管上的模拟值传输到像素存储器元件中。在Frame Overhead Time结束后,传感器将逐行读出。图像阵列操作和读出是流水线的。图像阵列操作在Row Overhead Time (ROT)中执行。在ROT序列期间,选择一个图像行进行读出。在积分开始时,顺序控制器在像素阵列上安排另一个全局操作。该序列称为Start of integration frame overhead sequence (SFOT)。在这个SFOT期间,读出将暂时停止。

在流水线快门模式下,积分时间是通过寄存器接口进行设置的(上述的SPI寄存器配置),传感器自主地积分并读取图像。如图所示,传感器无需任何用户交互即可获取图像。在高层次上,帧时间由非积分时间和积分时间组成(在此期间像素对光敏感并集成光线)。两个参数的总和是帧时间,以行周期的倍数配置。在总帧时间内,顺序控制器安排帧操作以启动和终止光积分。积分周期从Start-of-Integration FOT (SFOT)序列开始,以End-of-Integration FOT (EFOT)序列结束。请注意,SFOT和EFOT操作都需要一些时间,在此期间读出将停止。这将反映在传感器接口上的空闲期中。

1.3试验结果

最后,利用 FPGA对该驱动程序进行了实验,并给出了实验结果。

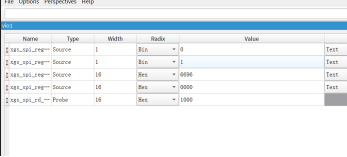

如图所示,通过SPI配置接口,对某一特定寄存器进行读数据的操作,传感器返回正确是数据,代表了传感器已经配置成功,而且已经正确输出了图像数据;

二、基于FPGA的图像存储处理设计

从具体的应用环境出发,选择了 CMOS芯片的pattern作为图像采集的输出;为满足传感器的数据时序,本方案使用了 易灵思公司生产的Trion FPGA芯片,使用 相关的EDA的开发工具 Efinity以及开源工具GTKwave一起完成了所有的设计、仿真和验证工作。

本方案将12路奇数行数据和12路偶数行数据经由interface designer 进行串并转换,将777.6Mbps的LVDS线上数据转成97.2Mbps的并行8bit数据,内部采用两个宽度96bit,深度4096bit的FIFO 进行奇数列和偶数列数据的缓存;根据BAYER图像转换算法,将sensor原始图像转换成RGB888的格式,并根据两行图像的数据量,按照地址递增的模式,依次将3072行数据按照AXI4的接口格式,传入到DDR3的控制器中,实现完整一帧图像的存储;将DDR3的地址分成3组,第一组反复存奇数帧图像,第二组反复存偶数帧图像,第三组存控制缓存数据;反复对图像数据进行写入和读取的操作,利用乒乓操作,在读取最新一帧图像的同时,将上一帧的数据从DDR3内读出发送出去,依次循环往复;将发出去的数据利用cypress 3014 可以自适应传输YUV数据格式,利用电脑相机功能就可以实时展现采集的图像数据;

三、结论

本文以安森美的XGS12000高精度和大分辨的CMOS传感器为研究对象,利用FPGA的LVDS接口多,速度快,实时性好的特性,进行处理,采用中等容量的memory进行缓存,最终发送到PC机上,得到分辨率可达4K@60fps的效果;同时,项目所开发的系统具有速度快、尺寸小、质量轻、集成度高、功耗低等优点,适用于空间环境下的成像测试。

参考文献:

[1]刘盼, 徐同伟, 张悦然. 基于FPGA的CMOS图像传感器接口设计与实现[J]. 北京工业大学学报, 2019, 45(09): 1215-1221.

[2]张慧, 杨夏玲, 李月宏. 基于FPGA的CMOS USB3.0图像传感器驱动设计[J]. 计算机工程与应用, 2020, 56(14): 73-77.

[3]杨朋飞, 刘宏超, 刘高峰. 基于FPGA的高速CMOS图像传感器驱动设计[J]. 电子产品应用, 2020(08): 46-49.

[4]肖靖雯, 陈军家, 蔡思源. 基于FPGA的CMOS图像传感器数据采集与预处理[J]. 海南师范大学学报(自然科学版), 2019, 32(02): 141-145.