中国电子科技集团公司第 38研究所 安徽 合肥 230031

【摘要】:本文介绍了基于成都振芯科技股份有限公司研发的双通道14位、1GSPS采样率ADC(Analog-to-Digital Converter)型号为GM4680-1000的模数转换芯片的多路高速宽带采集电路设计。该采集板卡具有2GHz模拟3dB输入信号带宽和转换速率高的特点。

【关键词】:ADC;数字下变频;信噪比

引言:

数字采集板作为雷达等电子装备的重要主要组成部分,主要实现对天线侦收的射频信号进行数字化转化功能。随着制造工艺和制程的进步,ADC的位数和转换速率也越来越高,目前国内的高速ADC主要依赖进口,由于中美贸易战的升级,高端ADC随时可能被禁用。本文介绍了一种采用国产ADC芯片GM4680搭建的多通道宽带数字采集板卡,板卡结构形式为6U ASAAC,已经在多个型号项目上应用。

1、硬件设计

根据Nyquist采样定理,采集电路最佳信号的中心频率f0和采样时钟fs关系应满足:

(M:任一正整数)

(M:任一正整数)

同时,采样频率至少大于等于2倍的信号带宽。根据大系统的性能指标要求该模块设计的信号带宽为400MHz,信号中心频率为750 MHz。因此选择采样时钟频率为1GHz。模块完成750MHz信号的采集、DDC预处理和高速传输。系统应用选择采样率为1000MHz,其量化位数是14bit。

ADC采用双通道高速ADC芯片GM4680-1000,其主要性能指标如下:

数据接口:4通道1.25Gbps~10Gbpds/lane JESD204B 接口(Subclass 1)

功耗:最大功耗3.3W

输入带宽:2GHz模拟3dB输入信号带宽

通道数:双通道最大2Vp-p模拟信号输入

采样率:1GSPS/500MSPS转换速率

分辨率:14位

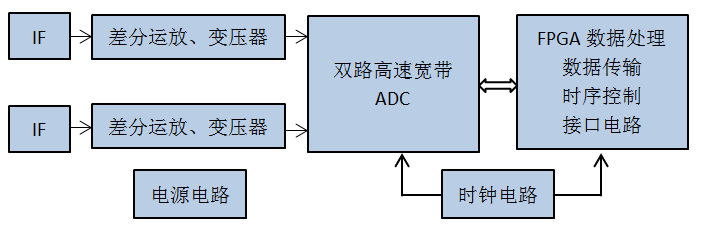

根据设计方案对电路进行原理图绘制,本设计中高速宽带采集模块使用的ADC芯片GM4680-1000设置为双通道独立工作,ADC的串行配置接口和JESD204B接口与FPGA相连。信号采用盲插连接器的接入方式,信号经变压器对电路进行阻抗变换后,形成差分信号再经低通滤波送ADC。板卡原理框图如下图所示。

图1 板卡原理框图

2、软件设计

ADC采样后的数字信号需做宽带数字下变频,2倍抽取后成500Msps的带基带I/Q数据。

对于数字化接收,目前广泛采用基于软件无线电设计思想的数字化接收机技术实现数字正交解调,用于实现解调的电路被称为DDC(Digital Down-Converter),具有NCO及可编程高效数字滤波器,因此在采样时钟确定的情况下,可在较宽范围内实现多种带宽信号的解调和匹配滤波。基本实现框图如下图所示。

图2 数字I/Q正交解调实现框图

图2 数字I/Q正交解调实现框图

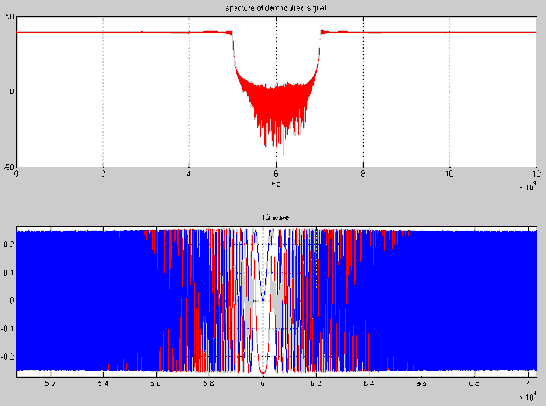

经过算法仿真得到的IQ信号频谱如下图所示:

图3基带IQ信号及其频谱图

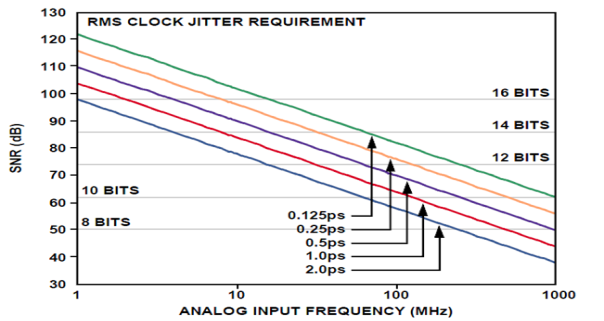

采样时钟孔径抖动对SNR的限制:

图4 理想信噪比和模拟输入频率及抖动的关系

高速、高分辨ADC对采样时钟的质量非常敏感。从上图可以看出,采样时钟的抖动必须在0.125ps以下才能保证理想信噪比不至于恶化到60dB以下。

电路的程序设计部分包括时序控制、电路配置、数据处理和数据传输。FPGA通过SPI三线串口(串行时钟SCLK、串行数据输入/输出SDIO、片选信号CSN)对ADC芯片的寄存器进行配置。SPI接口指令字宽为16bits,其中包括1位读写操作控制位和15位地址控制位,每个地址对应的数据位宽为8bits。

3、测试结果

原理图绘制完成后对印制电路板PCB设计,这里需要提前将器件进行草拟布局,同时要考虑电源以及信号的电磁扰动。设计过程中对使用的电源电流预估计算微带线宽度,部分高速传输线需要严格优化计算。本模块的PCB电路板采用了20层板工艺,有些高速数据传输通孔做了背钻处理,用于减小杂讯干扰和信号传输的反射、散射、延迟等。

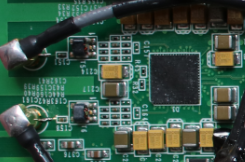

生产完成后的电路裸板实物ADC部分如图5所示。

图5 实物ADC部分图

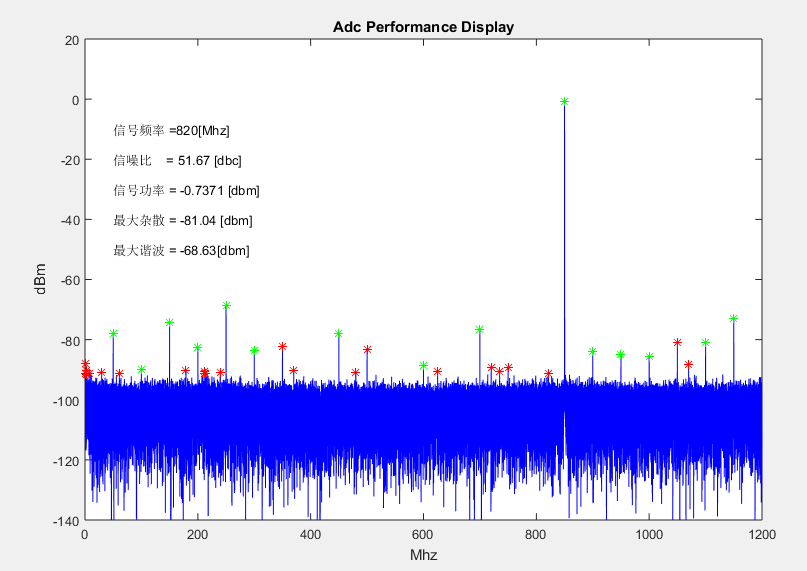

信号源设置为820MHz的连续波信号,功率输出为0dB进行了测试,信号源到采集板卡的电缆和连接器损耗约0.6dB。电路的测试结果通过MATLAB编写的分析软件可以很好的看出电路的各项指标。测试结果如图6所示。

图6 测试结果图

4、结束语

本文在基于ADC芯片GM4680-1000上进行了高速宽带采集模块设计,设计结果达到了较为理想的性能指标,电路长期工作参数稳定,故障率低。

参考文献:

[1] 吴霜毅,高速高精度采样/保持电路理论模型与技术实现[D],电子科技大学,2007.5

[2] 张俊杰,章凤麟,叶家骏,高速数据采集系统设计[J],计算机工程,2009,35(1):207-210

[3] 成都振芯科技股份有限公司,GM4680-1000/GM4680-500数据手册,2018